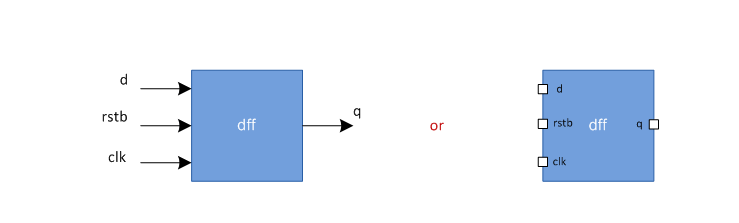

모듈( module ) 이란?

module은 Verilog HDL에서 설계하는 기본 단위입니다.

모듈은 독립적인 하드웨어 구성요소로, 입력(input), 출력(output), 회로 동작 등을 포함할 수 있습니다.

모듈은 다른 모듈에서 인스턴스화 될 수 있습니다.

인스턴스(instance) 란?

인스턴스(instance)는 Verilog HDL에서 모듈을 사용하는 방법 중 하나입니다.

인스턴스는 모듈을 복사하여 구현된 하드웨어 구성요소를 의미합니다.

모듈 인스턴스는 원래 모듈과 동일한 기능을 수행하며, 모듈과는 달리 구체화된 실제 하드웨어를 나타냅니다.

다음은 모듈과 인스턴스를 사용하여 간단한 2:1 멀티플렉서를 구현하는 Verilog HDL 코드 예제입니다.

// 2:1 멀티플렉서 모듈 정의

module mux2to1(

input a, b, sel,

output y

);

assign y = sel ? b : a;

endmodule

// 2개의 2:1 멀티플렉서를 사용하여 4:1 멀티플렉서 구현

module mux4to1(

input [3:0] data_in,

input [1:0] sel,

output reg y

);

wire [1:0] sel1;

wire [1:0] sel2;

wire y1;

wire y2;

// 하위 멀티플렉서 인스턴스 생성

mux2to1 mux1(.a(data_in[0]), .b(data_in[1]), .sel(sel1[0]), .y(y1));

mux2to1 mux2(.a(data_in[2]), .b(data_in[3]), .sel(sel1[0]), .y(y2));

// 상위 멀티플렉서 동작

always @(sel or sel1 or sel2 or y1 or y2) begin

sel1[0] = sel[0];

sel1[1] = sel[0];

sel2[0] = sel[1];

sel2[1] = sel[1];

mux1.sel = sel1[1];

mux2.sel = sel2[1];

if(sel1 == 2'b00) y <= y1;

else if(sel2 == 2'b00) y <= y2;

else y <= 1'bx;

end

endmodule

위의 예제 코드에서 mux2to1는 하나의 2:1 멀티플렉서를 나타내는 모듈이고, mux4to1은 두 개의 mux2to1 모듈을 인스턴스화하여 4:1 멀티플렉서를 구현하는 모듈입니다. 모듈(module)과 인스턴스(instance)는 Verilog HDL에서 가장 기본적인 구성 요소 중 두 가지입니다.

모듈(module)과 인스턴스(instance)는 Verilog HDL에서 가장 기본적인 구성 요소 중 두 가지입니다.

인스턴스는 모듈의 실제 복사본입니다. 인스턴스는 모듈의 특정 인스턴스를 식별하는 이름과 해당 모듈에 대한 포트 연결을 가지고 있습니다. 인스턴스는 모듈의 코드를 사용하여 설계를 구현하는 데 사용됩니다. 인스턴스는 모듈의 인스턴스화(Instantiation) 과정을 통해 생성됩니다.

예를 들어, 위에서 구현한 멀티플렉서 모듈을 사용하여 인스턴스를 생성하는 코드는 다음과 같습니다.

module top_module(

input a,

input b,

input sel,

output y

);

// 멀티플렉서 모듈 인스턴스화

mux_2to1 mux_inst(

.a(a),

.b(b),

.sel(sel),

.y(y)

);

endmodule위의 코드에서 mux_inst는 mux_2to1 모듈의 인스턴스입니다. 인스턴스 mux_inst는 a, b, sel 및 y와 같은 포트를 가지고 있으며, 각 포트는 mux_2to1 모듈의 해당 포트와 연결됩니다.

즉, 모듈은 설계의 일부분을 구현하는 데 사용되며, 인스턴스는 모듈의 실제 복사본입니다. 인스턴스는 모듈의 인스턴스화 과정을 통해 생성되며, 모듈의 코드를 사용하여 설계를 구현하는 데 사용됩니다.

'SoC > System Verilog' 카테고리의 다른 글

| [SystemVerilog] Modport와 Clocking block (4) | 2024.02.14 |

|---|---|

| [Verilog] initial begin 은 언제쓰일까? (0) | 2023.03.24 |