kksystem verilog 의 유튜브를 참고하여 정리해보았습니다.

https://www.youtube.com/@kksystemverilog5965

KK SystemVerilog

KK와 함께하는 System Verilog

www.youtube.com

VCS 란 ?

Synopsys사의 VCS, verdi 모두 degital 회로에서 검증 및 debugging용으로 쓰이는 tool입니다.

S사는 verdi를 쓰고 있으며, Cadence사의 xceilum 을 compiler로 씁니다.

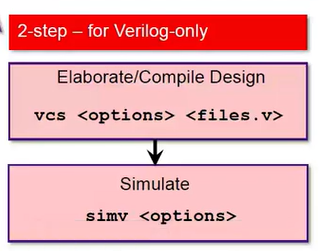

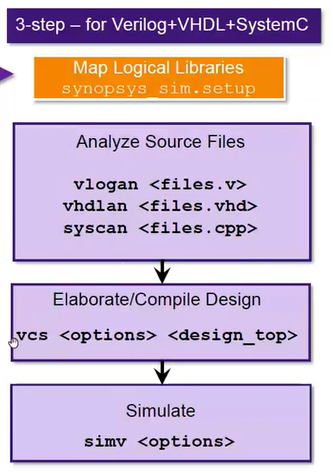

VCS flow overview

simulation하기 까지 단계는 다음과 같이 나누어져 있습니다.

Analysis

↓

Elab, Compile

↓

Simulation

Analysis : 코드의 문법 ( 세미콜론; , 오탈자 등) 체크합니다.

Compile : 코드를 해석하고 소스코드를 읽습니다.

Elaboration : 계충의 구조를 구축하고 신호들을 매핑하며 초기값을 계산합니다.

Simulation : 회로를 동작시킵니다.

VCS 절차까지

두가지 방법이 있습니다.

출처 : 유튜브 Kk system verilog

상 : 2단계 하 : 3단계(VHDL과 Verilog가 섞여있을 때)

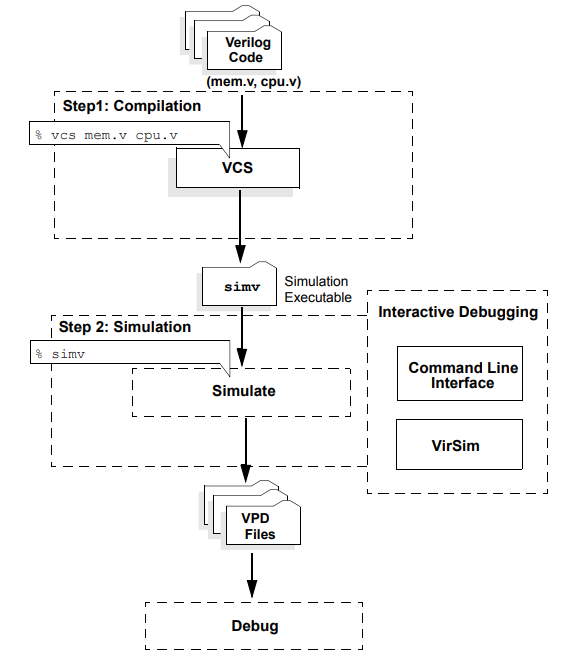

VCS flow

가장 기본적인 순서

1.License 얻기

2. 환경 세팅

setenv VCS_HOME 명령어로 VCS_HOME의 경로를 설정해야한다.

3. C compiler 세팅

Compile 시 option 리스트

|

-cm line | cond | fsm | tg1 | path | branch | assert

|

커버리지를 enable하고 타입을 정한다.

|

|

+cli+ [module_identifier=] level_number

|

command line interface command

|

|

+define+macro=value+

|

`ifdef 와 같이 macro를 설정하는 명령어

|

|

-f filename

|

path가 담겨있는 파일을 포함시키기

|

|

+incdir+directory+

|

`include 와 같이 경로를 특정하거나 파일을 포함시키기

|

|

+notimingcheck

|

timing check system을 무시한다.

|

|

-l

|

log file을 지정

|

|

-v

|

library file을 지정한다

|

|

-full64

|

64 bit mode simulation 진행 array가 32bit를 넘어설때 요즘 머신이 64bit라 보통 붙임

|

|

-o name

|

executable file을 특정한다.

|

|

-kdb

|

simulation 을 위해 kdb 파일 생성

|

|

-sverilog

|

systemverilog 언어 사용시

reg wire 혼성이 가능

|

|

-ucli

|

Tcl command line interface

중간 중간에 명령이 가능하게

|

|

-R

|

compile 후에 바로 simulation

|

|

-o <simname>

|

simv가 한 디렉토리에서 많이 생성되면 안되니까 simv이름을 바꿔주는 기능

|

-debug_access options

보통 -debug_access+all 의 형태로 씁니다.

SIMV option

|

-pv

|

parameter 를 정해줌

|

|

-gui

|

debugger 를 같이 띄움

|

|

-ucli

|

중간 중간 명령어 가능하게

|

실습하기

waveform 까지 띄우는 것을 목표로 하고 진행해보았습니다.

쓰인 예제는 counter 입니다.

위 : counter (DUT) 아래 : counter_tb (Testbench)

`timescale 1ns / 1ps

module Counter(

rst,

clk,

c

);

input rst;

input clk;

output [4:0] c;

reg [4:0] c = 5'h00;

always @ (posedge clk)

begin

if (rst)

begin

c <= 5'h00;

end

else

begin

if (c < 5'h13)

begin

c <= c + 1;

end

else

begin

c <= 5'h00;

end

end

end

endmodule`timescale 1ns / 1ps

module Counter_tb;

reg rst;

reg clk;

wire [4:0] c;

Counter DUT(

.rst(rst),

.clk(clk),

.c(c)

);

initial

begin

$dumpfile("Counter.vcd");

$dumpvars(0, Counter_tb);

rst = 1;

clk = 0;

#40

rst = 0;

#600

rst = 1;

#40

rst = 0;

#600

#20

$finish;

end

always

#10 clk = !clk;

endmodule

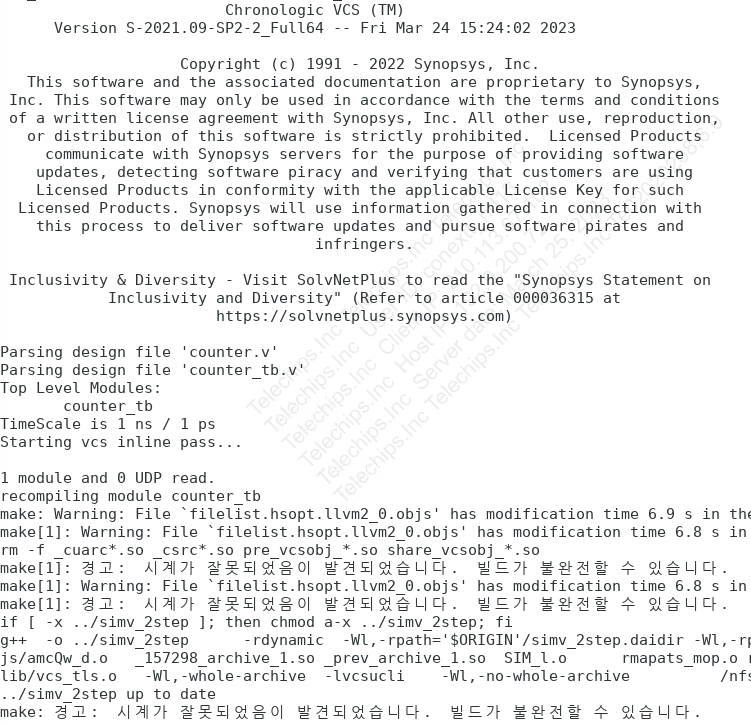

명령어를 치고 수행해보겠습니다.

.

.

.

오래걸리는 군요 ..

결과가 뜨고 이번엔 simv를 명령해봅니다.

VCS 명령어를 칠때는 top이름을 지정해야합니다.

-top test ( test 가 top 파일)

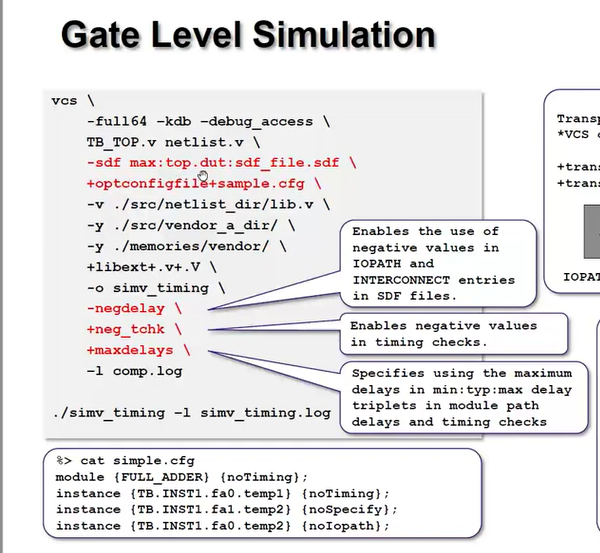

Gate level simulation

위와 같이 명령어를 취하면 됩니다.

특정한 모듈이나 인스턴스 조건을 걸 시

+optconfigfile+sample.cfg 조건을 겁니다.

negdelay : negative delay가 존재할 시에는 vcs가 0으로 만든다. 0을 안만들겠다 하면 이 옵션을 추가합니다.

neg_tchk : negative delay를 관찰하고 싶을때 negative delay가 tcheck 파일에 저장이 됩니다.

+transport_path_delays : module path delay를 enable

+transport_int_delays : net delay를 enable

+notimingcheck : timing check를 없앱니다.

+sdfverbose : 모든 정보들을 출력합니다.

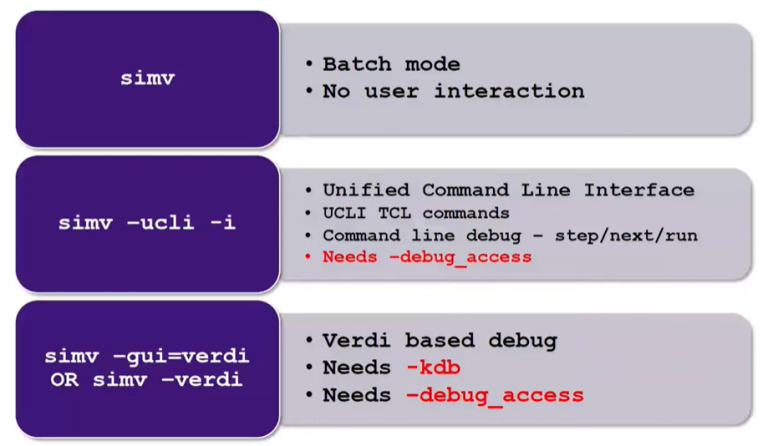

Simulation modes

simv 간단한 option 들.

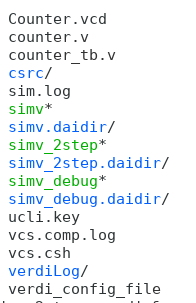

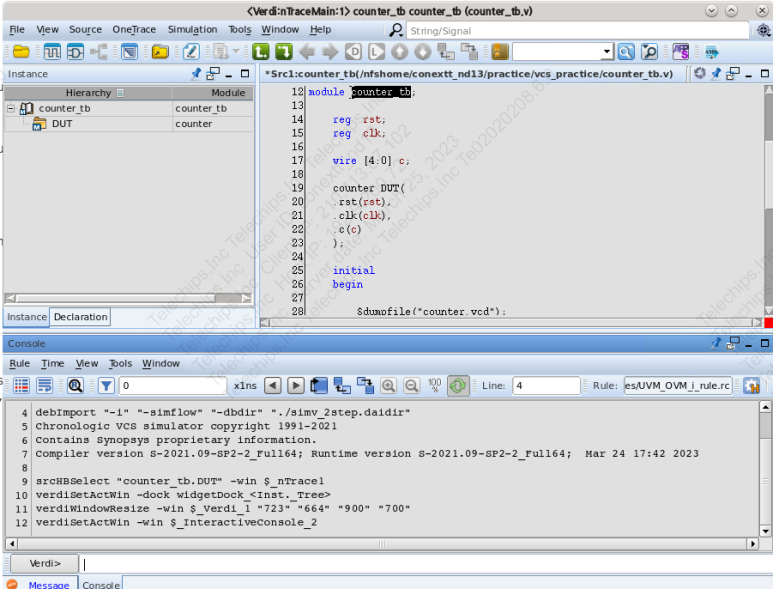

VCS 를 통해 simv 를 생성했습니다.

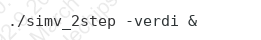

위 명령어를 쓰면

위 창이 뜨게 됩니다.

위를 통해 waveform 을 관찰할 수 있습니다.

Waveform은 다음 시간에 하도록 하겠습니다.

'SoC > Tool' 카테고리의 다른 글

| [DV] Synopsys'coverage / VCS coverage / 커버리지란? / 커버리지 종류 (0) | 2023.03.28 |

|---|